## TP 4 : Mémoires (à rendre à la fin de la séance)

## Rappels

La mémoire est un composant permettant de stocker des valeurs binaires. On distingue les mémoires à lecture seule dites ROM (Read-Only Memory) et à lecture/écriture dites RAM (Random-Access Memory). Le contenu d'une ROM est initialisée à l'usinage et par conséquent persistent. Au contraire, la RAM est volatile, c'est à dire que son contenu est perdu lorsqu'elle n'est plus alimentée.

Il existe des mémoires statiques (SRAM) et dynamiques (DRAM) distinguées par leur technique de fabrication. La mémoire statique est caractérisée par des opérations rapides et par conséquent un coût onéreux, on l'utilise donc pour implanter des caches. La mémoire dynamique est caractérisée par des opérations lentes et par conséquent un coût bon marché, on l'utilise donc pour implanter la mémoire principale.

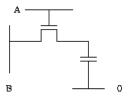

Chaque élément de mémoire dynamique est formé d'un condensateur et d'un transistor de commande (cf. figure ci-dessous). La ligne A est appelée ligne de commande ou ligne d'adresse. La ligne B est la ligne de donnée sur laquelle est lu ou écrit le bit d'information. Le bit d'information est représenté par la charge du condensateur. Lorsque la ligne de commande est à 0, le condensateur est isolé de la ligne de donnée et la charge reste prisonnière du condensateur. Au contraire, lorsque la ligne de commande est à 1, on peut lire le bit en détectant la charge ou écrire un nouveau bit en forçant la ligne de donnée à une valeur.

FIGURE 1 – Mémoire dynamique

L'élément de base de la mémoire s'appelle un point-mémoire (et correspondra pour nous à une bascule). Un regroupement de points-mémoire forme un bloc-mémoire, et permet de stocker un mot (e.g. un bloc de 8 bascules permet de stocker un mot de 8 bits, c'est-à-dire un octet). Dans la suite de ce TP, nous nous intéresserons à réaliser une **mémoire statique**. À la place d'un transistor de commande (composant analogique), nous utiliserons un **tri-buffer** (composant logique).

${f Note}$ : Un solution partielle documentée et propre sera bien évidemment préférable à une solution globale mais illisible. Par exemple, un afficheur hexadécimal pour la sortie S et un interrupteur hexadécimal pour l'entrée V seront fortement appréciés.

## Les registres

$ouf,\ c'est\ pas\ ceux\ des\ imp\^ots.$

Le but de cet exercie est de construire un bloc-mémoire de type RAM statique, constitué par 4 mots de 4 bits chacun.

- 1. Construire un point-mémoire (ou registre 1 bit) à partir d'une bascule flip-flop D. On pourra utiliser les bascules D de TkGate. On rappelle que celles-ci disposent :

- $\bullet$  de l'entrée usuelle D;

- d'une entrée clock (représentée par un triangle), telle que la mise à jour se fait sur front montant ;

- d'une entrée clear, notée  $\overline{C}$ , qui permet d'initialiser la bascule à zéro lorsque  $\overline{C} = 0$ ;

- d'une entrée enable, notée  $\overline{E}$ , telle que la bascule est mise à jour uniquement si  $\overline{E}=0$

- des deux sorties usuelles Q et  $\overline{Q}$ .

Le circuit sera asynchrone (c'est-à-dire sans horloge) et devra contenir, en plus des entrées du bit de donnée, clear et enable, une entrée RW permettant de choisir le mode (lecture/écriture) et une entrée CS (chip select) permettant d'activer ou désactiver le point-mémoire.

- 2. En utilisant le stable à trois états (le *tri-buffer*), réaliser un registre 1 bit tel qu'une seule connexion est utilisée à la fois pour l'entrée et pour la sortie. L'entrée-sortie sera représentée par un interrupteur et une diode sur une même connexion. Avec une bonne utilisation du tri-buffer, l'activation de *CS* lors du mode lecture "forcera" en sortie l'interrupteur et la diode sur la valeur en mémoire.

- 3. Réaliser un module TkGate correspondant à un mot de 4 bits. Utiliser ces modules pour constituer une RAM de 4×4 bits. L'adressage se fera par des commandes extérieures, utilisées dans un module de type multiplexeur <sup>1</sup>, qui permettra de choisir le mot à lire ou écrire parmi les quatre mots. On rajoutera une commande *OE* (output enable) qui permettra, en mode lecture, de laisser passer les sortie (celles-ci forceront ainsi la valeur des connexions communes d'entrée/sorties). Cette commande *OE* permet d'éviter les parasites entre l'entrée et la sortie. Au final, le circuit devra donc comporter :

- les quatre connexions d'entrées/sorties;

- les commandes d'adresses;

- la commande clear et la commande enable communes à toutes les bascules D;

- la commande RW de lecture/écriture;

- la commande CS (chip select) qui permet de selectionner le boitîer;

- la commande OE (output enable).

## Pile

$En(e(rg(\{i\}ze))r)$

Dans cette exercice vous allez modéliser une pile. Pour cela vous devez utiliser le module RAM  $8\times 8$  de TkGate (8 bits d'adresse et 8 bits de donnée par adresse). Ce module comporte les 3 entrées comme dans l'exercice précédent :  $\overline{CS}$ ,  $\overline{OE}$ ,  $\overline{WE}$  (ce dernier est appelé RW précédemment); une entrée 8 bits A qui correspond aux adresses des blocs mémoire; une sortie 8 bits D qui représente la sortie ou l'entrée en fonction des valeurs des  $\overline{CS}$ ,  $\overline{OE}$  et  $\overline{WE}$ .

- 1. Réalisez un module compteur/décompteur modulo 256 synchronisé sur une horloge <sup>2</sup>. Le module doit avoir une entrée qui, à chaque front montant, compte lorsque elle est à 0 et qui décompte sinon. Vous êtes encouragés à réutiliser un additionneur et un registre (sur 8 bits tous les deux) de TkGate.

- 2. Utilisez le module précédent et la RAM pour simuler le fonctionnement d'une pile. Le circuit comportera une seule sortie S sur 8 bits et deux entrées :

- Empiler/Dépiler sur 1 bit

- V sur 8 bits

L'opération Empiler correspond à : la valeur V (définie par l'utilisateur) est écrite à l'adresse mémoire courante, puis cette adresse est incrémentée de 1.

L'opération Dépiler correspond à : l'adresse mémoire courante est décrémentée de 1, puis la valeur à la nouvelle adresse est affichée sur la sortie S.

Astuce : Si vous n'arrivez pas à réaliser le fonctionnement intégral, des solutions partielles réalisant exclusivement les empilements ou les dépilements seront tout de même considérées dans l'évaluation.

<sup>1.</sup> Vous pouvez ré-utiliser le multiplexeur de  ${\tt TkGate}.$

<sup>2.</sup> On paramètrera l'unité de temps de la simulation à 10sec, la précision à 1sec et la durée du cycle de l'horloge à 50.